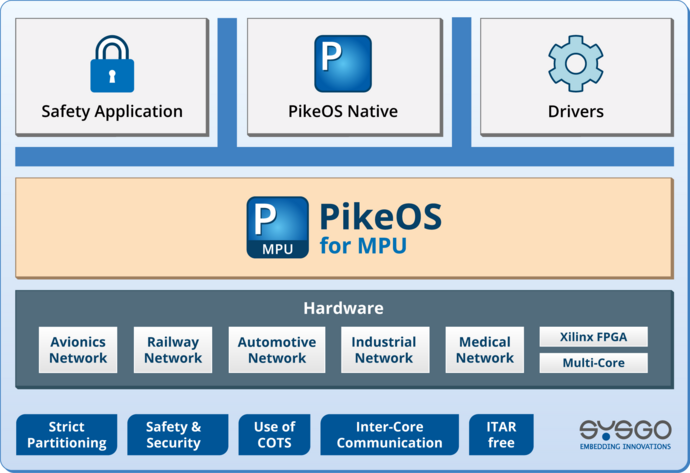

PikeOS for MPU

Real-Time Partitioning for MPU Architectures

- Based on a separation kernel with the performance of a traditional RTOS

- Available to lightweight systems with a Memory Protection Unit (MPU) only

- For controllers targeting Medical, Automotive, Aeronautics and Space industries

- Easing and accelerating certification for Safety-critical systems

- Reduces hardware requirements and complexity

Application Separation

PikeOS offers strict partitioning and strong separation to provide built-in Security by design

Hardware Consolidation

Extreme flexibility provides independence from suppliers in the choice of hardware architectures

Use of COTS

The benefit of using Commercial-Off-The-Shelf (COTS) components is to lower overall costs for applications

PikeOS Compatibility

+80% of the original code base makes the available PikeOS documentation and certification artefacts reusable

Inter-Core Communication

PikeOS instances on different cores can communicate with each other via message-based communication channels

ITAR-free

As European company, our products have no export restrictions enabling unrestricted global deployment

PikeOS for MPU

PikeOS for MPU is aiming to provide a safe and secure execution environment for medium-sized hardware platforms which do not provide a Memory Management Unit (MMU) and therefore cannot run the standard PikeOS.

PikeOS for MPU is intended to be used on MPU-based SoCs as well as on heterogeneous SoC implementing MMU and MPU clusters.

We continually enhance and update PikeOS for MPU to meet evolving technology and industry requirements.

What's new with PikeOS for MPU 1.1

Have a look at the features and updates of our latest PikeOS for MPU version.

Development Environment and APIs

you have been used to

There is almost no learning curve, as the development tools and API stay nearly identical. PikeOS for MPU is embedded into CODEO as if it was just another architecture. That also makes migration from older applications remarkably simple. PikeOS Classic and PikeOS for MPU projects can even be managed in the same IDE at the same time.

Since the development tools, such as the ROM-Image builder and the VMIT (Virtual Machine Initialization Table) builder, are shared between the two operating systems, PikeOS for MPU inherits the qualification status of its bigger brother. That together with the fact that PikeOS for MPU bases on SYSGO's well-proven virtualization technology, PikeOS for MPU comes with a head start in terms of certification.

PikeOS & PikeOS for MPU

working Hand in Hand

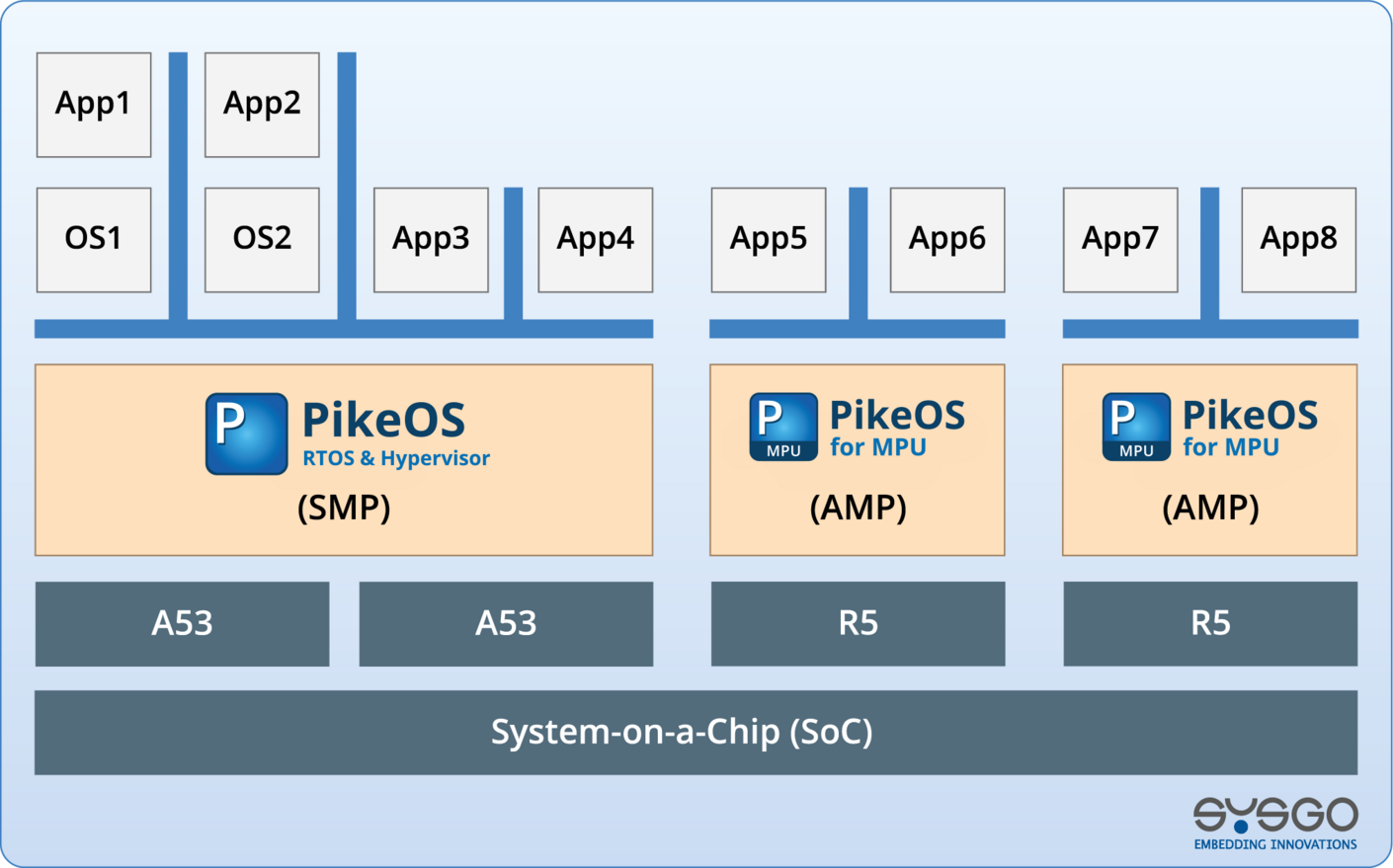

Multi-core processors have entered the embedded market. However, unlike to desktop computing where all processor cores are of the same type,

embedded SoCs (Systems-on-a-Chip) are highly specialized for a dedicated purpose. Therefore, you will often find heterogeneous processor cores on the same chip.

With the PikeOS family of products, you can manage the entire software stack of such a complex big SoC within one single CODEO workspace. The project wizards and editors support you while you are planning the architecture of AMP and SMP domains. Even anything in between can be designed.

A typical setup on a Xilinx Ultrascale+ would look like as shown in the architecture:

PikeOS is running multiple partitions on the Cortex-A53 cores in SMP (Symmetric Multi-Processing) mode, while the Cortex-R5 cores are executing PikeOS for MPU in AMP (Asymmetric Multi-Processing) mode.

During your development it might turn out that the current assignment of software applications to processor cores is not optimal. Fortunately, this can be fixed with almost no efforts, as the PikeOS solution allows you to utilize the same API, no matter whether the CPU provides an MMU or MPU.

PikeOS for MPU

Starting into the Multi-Core World

PikeOS for MPU is based on the same time- and resource partition management as the classic PikeOS operating system. It also shares the same internal, fine-grained locking mechanisms and has the same means to mitigate hardware interference between processor cores, e.g. due to cache contention. The system integrator has all methods at his disposal to determine the worst-case execution times and enforce that any application does not consume more processor usage than it is allowed. Together with our partner eco system, PikeOS for MPU is ready for Safety-related standards on multi-core processors, such as CAST-32A.

PikeOS for MPU in Space

Reducing Single Event Upset (SEU) Effects

The environment in space is harsh, not only in terms of temperature and vibration, but also due to cosmic radiation. One of the major goals is to reduce and mitigate the effects of a single event upset. That is why hardware for space missions is stripped down in complexity. Boards based on processors without an MMU are way less complex, easier to understand and better to protect. We are proud to say that one of the first projects and our motivation to build PikeOS for MPU lies in the support of Space missions.

Cybersecurity by Design

for Mixed Criticality embedded Systems

Software Security Requirements

- Protection of the OS layer from applications, and applications from other applications

- Protection of the communication to and from external systems

- Secure Boot / Secure Update of systems

PikeOS for MPU has a pre-qualified set of documentation for Security and provides the basis to provide all Security features to be used for SBRTOS (Systems Based on the RTOS).

For Security certification on system level, the combination of the NG-ULTRA SoC FPGA (Field Programmable Gate Array) and PikeOS for MPU have the best pre-requisites to fulfill the needed requirements for Space missions concerning Security while maintaining Safety and dependability.

Our key drivers are the re-usability and ability to support the Space Avionics Open Interface Architecture (SAVOIR).

Ready for Space Security

PikeOS for MPU ensures the separation of applications by means of time and space partitioning. A partition is created and maintained by the operating system and resources are allocated according to the partition configuration, like memory, CPU time or I/O access rights.

PikeOS for MPU has been validated with respect to Security and Common Criteria or a similar approach can be used as Security standard.

SYSGO in the Knowledge Bank of ESA’s R&D Programmes

The project aim is to create a real-time operating system tailored for spacecraft microprocessors. It has to meet rigorous Security and Safety standards, allowing it to run multiple applications simultaneously, each with varying levels of assurance (mixed criticality), while ensuring Safety and Security.

PikeOS for MPU and the Cyber Resilience Act (CRA)

Security requirements under the Cyber Resilience Act (CRA) also apply to microcontroller-based devices — where resources are tight but risks are real. PikeOS for MPU brings the proven Security architecture of PikeOS to MPU-class hardware, sharing around 80% of the same mature, field-proven codebase. Discover how PikeOS and PikeOS for MPU support CRA-ready embedded development.

PikeOS for MPU and ESA

Space Avionics Open Interface Architecture (SAVOIR)

SAVOIR is an initiative of the European Space Agency (ESA) aimed at uniting the Space Avionics community and working together to improve the way European Space community builds Avionics subsystems.

SAVOIR Main Objectives:

- Reduction of schedule and risk, along with associated costs, for the procurement and development of Avionics

- Enhancement of competitiveness of Avionics suppliers

- Influence on standardization processes by standardizing at the appropriate level to ensure device interchangeability (the topology remains project-specific)

- Definition of the governance model for products, generic specifications, and interface definition of elements developed under the SAVOIR initiative

SAVOIR is applied as part of ESA tenders and throughout the subsequent procurement and development process. A particular aim is to utilize the results of SAVOIR in future projects and relevant products as part of the portfolios of European suppliers.

SAVOIR expected Benefits:

- For customers: Simplification of the procurement process for Space Avionics

- For system integrators: Facilitation of space avionics integration

- For suppliers: Preparation of technical conditions for more efficient product line organization

SAVOIR supports:

- Space Avionics customers and system architects

- System integrators

- Avionics and technology suppliers

- Standardization organizations

It is a tool for industrial policy and research and development planning. For further information, please visit www.savoir.estec.esa.int

Professional Support

We provide two types of product support: The Standard Support covers the basic questions on the product use (installation, tools usage etc.) via E-Mail. The Premium Support offers more customer-specific help with direct contact to a dedicated support engineer.

Life Cycle Updates

Customers can benefit from ongoing improvements by accessing the SYSGO customer portal, where the latest updates of target binaries, new Board Support Packages, and add-ons are available.

Training & Consulting

We want to make building your target devices as convenient as possible. However, SYSGO’s guided trainings boost the skills of your embedded developer team and maximizes the output – for efficient teams that love to develop for embedded devices.

Customer Benefits

Ultimate SWaP-C Optimization for Edge Devices

PikeOS for MPU is engineered for hardware without a Memory Management Unit (MMU), allowing you to implement Safety-critical partitioning on low-power, low-weight, and low-cost microcontrollers. This is the key to reducing Space, Weight, Power, and Cost in applications like satellites, medical patches, and distributed industrial sensors where every milliwatt and gram counts.

Fast-Boot & Deterministic Real-Time Response

By eliminating the overhead of virtual memory management, PikeOS for MPU achieves ultra-fast boot times (often in the millisecond range) and the highest level of execution determinism. This ensures that your system is "ready-to-act" immediately after power-on, which is critical for Safety functions in Automotive ECUs and high-speed industrial shut-off systems.

Operational Flexibility: Adaptive Multi-Schedule Switching

Modern embedded systems often need to behave differently depending on their current mission phase (e.g., an EV in "Charging Mode" vs. "Driving Mode," or a satellite in "Safe Mode" vs. "Payload Operation"). PikeOS for MPU allows you to define multiple, pre-validated scheduling schemes that can be switched dynamically at runtime. This "adaptive scheduling" ensures that your CPU resources are always prioritized for the most critical tasks of the current phase, optimizing performance without ever violating the strict time-partitioning required for Safety certification.

Inter-Core Communication (ICCOM) for Heterogeneous SoCs

In modern "Big-Little" or heterogeneous SoC architectures (like Xilinx Zynq UltraScale+), PikeOS for MPU enables seamless, secure communication between real-time R-cores and application A-cores. With the PikeOS family, you can manage your entire software stack within a single CODEO IDE workspace. This allows you to build sophisticated systems where high-level Linux logic and hard real-time Safety tasks work in perfect, isolated harmony.

80% Code Reuse & Unified Development Ecosystem

PikeOS for MPU shares over 80% of its code base and the same API as the standard (MMU) PikeOS. This allows your team to seamlessly port applications between high-end SoCs and smaller microcontrollers. You can manage your entire heterogeneous system—combining MMU and MPU cores—within a single CODEO IDE workspace, drastically reducing learning curves and development overhead.

Space-Grade Reliability & SEU Mitigation

Specifically optimized for the harsh conditions of space and high-altitude environments, PikeOS for MPU's simplified architecture is inherently more resistant to Single Event Upsets (SEUs). Its robust health monitoring and error-handling frameworks detect and isolate hardware faults at the partition level, ensuring mission success even when cosmic radiation strikes.

MILS Architecture on Microcontrollers

Bring Multiple Independent Levels of Security (MILS) to the microcontroller level. PikeOS for MPU ensures that sensitive Security functions (like crypto-key management) are strictly isolated from less critical communication tasks. This prevents a "lateral movement" attack, where a compromised network stack could otherwise take control of the entire device.

European Sovereignty & ITAR-Free Global Reach

Like all SYSGO products, PikeOS for MPU is developed in Europe and is entirely free from U.S. ITAR export restrictions. This allows you to integrate High-Security separation kernel technology into products destined for global markets without the administrative burden or geopolitical risks associated with foreign-controlled software.

Seamless Compliance with the EU Cyber Resilience Act (CRA)

The CRA mandates security-by-design and lifecycle vulnerability management for all digital products in the EU. PikeOS for MPU provides a pre-certified, secure foundation that simplifies your path to compliance. By using a kernel that already implements strict MILS separation and secure update mechanisms, you reduce the legal and engineering burden of proving your device’s resilience from deployment to end-of-life.

Long-Term Maintenance & Life Cycle Support

Critical systems often have lifespans of 15 to 30 years, far outlasting standard consumer technology. SYSGO provides long-term support and maintenance services that guarantee the availability of Security patches and technical expertise for the entire duration of your project. We act as a long-term partner, ensuring your system remains safe and secure from deployment to decommissioning.